# STRAWBERRY

[] /strawberrydevelopers

[] /strawberry\_app

For more visit:

Strawberrydevelopers.weebly.com

## INTERFACING

Richa Upadhyay Prabhu

NMIMS's MPSTME

richa.upadhyay@nmims.edu

February 25, 2016

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへぐ

## 8255: Programmable Peripheral Interface or Programmable Input output Device

#### Introduction

#### METHODS OF DATA TRANSFER

- Simple Input and Output

- Simple Strobe Input/ Output

- Single Handshake data transfer

- Double Handshake data transfer

▲ロト ▲御 ト ▲ 臣 ト ▲ 臣 ト の Q @

#### Simple Input and Output

I/O operations are not directly dependent on any other signals. For Example: Reading data from thermostat; it is simple connected to input port line and processor simply reads the port, as data is always available and ready so it can be read any time.

The crossed lines on the waveform represents time at which data byte is available at the port

(日) (同) (三) (三) (三) (○) (○)

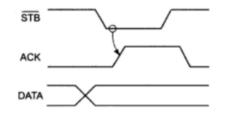

## Strobe Input and Output

- This mode is used when valid data is present on the port only at a certain time, and needs to be read at that time.

- External device sends a strobe signal to indicate valid data is present on the data lines.

- Strobe can be connected to interrupt input

- Transfer is time dependent

#### Strobe Input and Output

- High speed data transfer not possible

- data rates of sending system and receiving system can be different

• to avoid this HANDSHAKE data transfer is used

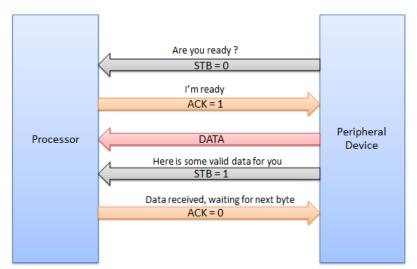

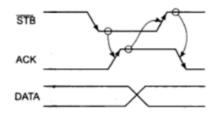

## Single handshake I/O

#### Handshake Data Transfer

- Peripheral device outputs some data and sends strobe signal to processor

- Processor detects strobe on poll or interrupt basis and reads the data

- Also it sends an Acknowledge signal to device indicating that data has been read and next byte of data can be sent.

## Double Handshake Data Transfer

• Used where more co-ordination is required

#### Double Handshake Data Transfer

◆□ > ◆□ > ◆ □ > ◆ □ > □ = のへで

Handshaking is a good idea but uses too much processor time, so parallel port devices such as 8255 are used to automatically manage handshake operation.

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 の�?

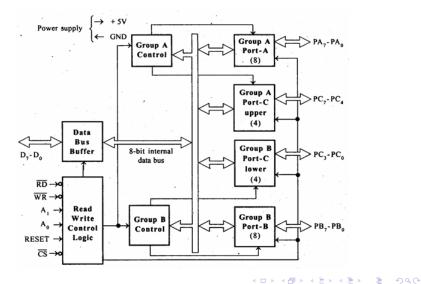

## 8255 Programmable Peripheral Interface

- It is a programmable parallel I/O device

- 40 pin IC

- 24 programmable I/O pins arranged as two 8-bit ports and two 4-bit ports

- It has Three 8-bit ports: Port A,Port B and Port C, which are arranged in two groups of 12 pins

- Control register defines the functions of each I/O port and in which mode they should operate

#### Pin Diagram

40 PA, PA, + D<sub>0</sub> - D 39 PA, PA, ← - PA > PA PA; ↔ 38 8  $\frac{PA_0}{RD}$  $\overline{CS}$ 37  $\rightarrow$  PA, WR 36 RD-RESET 35  $V_{ss}$ WR-34 D. PC, - PC 33 → D. Α, 8255A 8255A A,-32 A, D, 31 PC, ↔ 10 D, A<sub>0</sub>- $PC_{6} \leftrightarrow$ 30  $\leftrightarrow D_{i}$ 29 PC, () 12 ↔ D, PC<sub>1</sub> - PC<sub>0</sub> RESET 28 PC, ← 13 D,  $PC_{o} \leftrightarrow 14$ 27 D, cs -26  $V_{cc}$ PC, ↔ 15 25 PB,  $PC, \leftrightarrow 16$ (+5V)V<sub>cc</sub> 24 PB<sub>6</sub> PB, - PB PC, ← 17 23 PB<sub>0</sub> ↔ 18  $\leftrightarrow PB_{i}$ (0V)V<sub>ss</sub> 22 PB<sub>1</sub> ↔ 19 PB, 21 PB,  $PB_2 \leftrightarrow 20$

#### Pin Diagram Description

- PA0- PA7 : Port A; 8-bit bidirectional I/O pins

- $PB_0$   $PB_7$ : Port B; 8-bit bidirectional I/O pins

- $PC_{0}$   $PC_{7}$ : Port C; 8-bit bidirectional I/O pins. These can even be used as two 4-bit ports ( $PC_{0} - PC_{3}$  and  $PC_{4} - PC_{7}$ ), Also used to produce handshake signals for A and B

- $D_0 D_7$ : 8-Bit bi-directional data bus connected to processor

- RESET : When reset clears control word and all ports

- *RD* : Read, active low input line used to read data from processor

- *WR* : Write, active low input line used to send data to processor

#### Pin Diagram Description

#### $A_0 - A_1$ : Address Lines; used to select ports of 8255

| $A_0$ | $A_1$ | Selected Port    |  |  |  |

|-------|-------|------------------|--|--|--|

| 0     | 0     | Port A           |  |  |  |

| 0     | 1     | Port B           |  |  |  |

| 1     | 0     | Port C           |  |  |  |

| 1     | 1     | Control Register |  |  |  |

#### 8255 Functional Block Diagram

## 8255 Operational Modes and Initialization

MODE 0

- simple input or output without handshaking

- If Port A and B are initialized in mode 0, port C can be used as 8-bit port

- If port C lines are used as output, individual bits can be set and reset by special control word

- Two halves of port C (4-bits)are independent

- One can be used as input and other as output

## 8255 Operational Modes and Initialization

#### MODE 1

- Use port a or B as handshake(strobed) input/output

- PC<sub>0</sub>, PC<sub>1</sub>, PC<sub>2</sub> lines of port C are used as handshake lines for port B

- *PC*<sub>3</sub>, *PC*<sub>4</sub>, *PC*<sub>5</sub> lines of port C are used as handshake lines for port A(input port)

- PC<sub>6</sub>, PC<sub>7</sub> lines are used as input output lines

- PC<sub>3</sub>, PC<sub>6</sub>, PC<sub>7</sub> lines of port C are used as handshake lines for port A(output port)

- $PC_4$ ,  $PC_5$  lines are used as input output lines

## 8255 Operational Modes and Initialization

MODE 2

- Bi-directional handshake data transfer

- Data can be output or input on the same eight lines

- If port A is used in mode 2 :

- $PC_3$  to  $PC_7$  are used as handshake line for port A

- $PC_0$  to  $PC_2$  can be used as I/O pins if Port B is in Mode 0

- Or PC<sub>0</sub> to PC<sub>2</sub> are used as port B handshake if Port B is in Mode 1

## 8255 Control word (8-bit)

There are two types of Control word:

The MSB tells which control word is being sent

- Mode definition control word (if MSB = 1)

- 2 Port C bit set/reset control word (if MSB = 0)

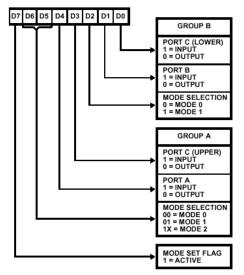

#### Mode definition control word (if MSB = 1)

▲□ > ▲圖 > ▲ 臣 > ▲ 臣 > → 臣 = ∽ 9 Q (?)

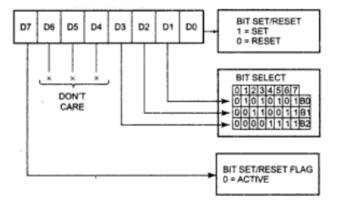

#### Port C bit set/reset control word (if MSB = 0)

◆□> <圖> < => < => < => < => < <</p>

## 8254 Software Programmable Timer/Counter

▲ロト ▲帰 ト ▲ ヨ ト ▲ ヨ ト ・ ヨ ・ の Q ()

Why 8253/8254? Since, it is not possible to generate accurate time delays Using delay subroutines in 8086.

8254/8253 facilitates:

- Accurate time delays

- Minimizes load on processor

- real time clock

- event counter

- square wave generator

- complex waveform generator

Software Programmable Timer/Counter means, we can load count in them, start them and stop them with instructions in the program.

To program such device, COUNT BYTES and CONTROL BYTES have to be sent to the timer/counter peripheral device

#### 8254 vs 8253

| 8253                   | 8254                 |

|------------------------|----------------------|

| clock frequency 2.6MHz | clock frequency 8MHz |

| No wood hools footune  | Deed heals feature   |

| No read back feature   | Read back feature    |

Read back feature allows to latch the count in all counters and the status of counters at any point.

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへぐ

#### Features of 8254

- Three independent 16-bit down counters.

- 8254 can handle inputs from DC to 10 MHz (5MHz 8254-5, 8MHz 8254, 10MHz 8254-2) where as 8253 can operate upto 2.6 MHz

- Three counters are identical presettable, and can be programmed for either binary or BCD count.

- Counter can be programmed in six different modes.

- Compatible with all Intel and most other microprocessors.

- 8254 has powerful command called READ BACK command which allows the user to check the count value, programmed mode and current mode and current status of the counter.

◆□ > ◆□ > ◆豆 > ◆豆 > ̄豆 = のへで

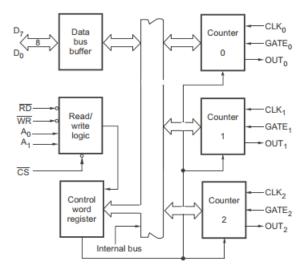

Data Bus Buffer :

• Bi-directional, 8-bit buffer is used to interface the 8253/54 to the system data bus.

- The Data bus buffer has three basic functions:

- Programming the modes of 8253/54.

- Loading the count registers.

- Reading the count values.

Read/Write Logic : The Read/Write logic has five signals :  $\overline{RD}, \overline{WR}, \overline{CS}$  and the address lines A0 and A1

In the peripheral I/O mode, the RD, and WR signals are connected to IOR and IOW, respectively. In memory-mapped I/O, these are connected to MEMR and MEMW

| A <sub>1</sub> | A <sub>0</sub> | Selection             |

|----------------|----------------|-----------------------|

| 0              | 0              | Counter 0             |

| 0              | 1              | Counter 1             |

| 1              | 0              | Counter 2             |

| 1              | 1              | Control word Register |

Control Word Register :

- This register is accessed when lines A0 and A1 are at logic 1

- used to write a command word which specifies the counter to be used (binary or BCD), its mode, and either a read or write operation.

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへ⊙

Counters :

- These three functional blocks are identical in operation.

- Each counter consists of a single, 16 bit, pre-settable, down counter.

- Can operate in either binary or BCD

- Its input, gate and output are configured by the selection of modes stored in the control word register

• Programmer can read the contents of any of the three counters without disturbing the actual count in process

Counters :

- $\mathsf{CLK}\,$  : Signals of frequency between 0 to 8 MHz can be applied as input to these 3 pins

- GATE : Allows to start or stop the counter with an external hardware signal. If GATE = 1, counter is enabled for countig and if GATE = 0 it is disabled.

- OUT : Output signal of each counter appears on this pin.

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへぐ

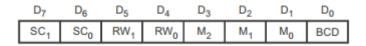

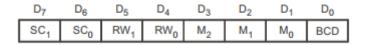

#### SC - Select counter

SC1 SC0

| 0 | 0 | Select counter 0                                                         |

|---|---|--------------------------------------------------------------------------|

| 0 | 1 | Select counter 1                                                         |

| 1 | 0 | Select counter 2                                                         |

| 1 | 1 | Illegal for 8253<br>Read -Back command for 8254<br>(See Read operations) |

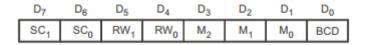

| _ | D <sub>7</sub>  | D <sub>6</sub>  | D <sub>5</sub>  | D <sub>4</sub>  | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|---|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|

|   | SC <sub>1</sub> | SC <sub>0</sub> | RW <sub>1</sub> | RW <sub>0</sub> | M <sub>2</sub> | M <sub>1</sub> | Mo             | BCD            |

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 の�?

#### M - Mode

M<sub>2</sub> M<sub>1</sub> M<sub>0</sub>

| 0 | 0     | Mode 0            |

|---|-------|-------------------|

| 0 | 1     | Mode 1            |

| 1 | 0     | Mode 2            |

| 1 | 1     | Mode 3            |

| 0 | 0     | Mode 4            |

| 0 | 1     | Mode 5            |

|   | 0 1 1 | 0 1<br>1 0<br>1 1 |

▲□▶ ▲圖▶ ▲臣▶ ▲臣▶ ―臣 … のへで

#### RW - Read /Write

RW<sub>1</sub> RW<sub>0</sub>

| 0 | 0 | Counter latch command<br>(See Read operations)                           |

|---|---|--------------------------------------------------------------------------|

| 0 | 1 | Read / Write least significant byte only                                 |

| 1 | 0 | Read / Write most significant byte only                                  |

| 1 | 1 | Read / write least significant byte first,<br>then most significant byte |

#### 8254 Control Word Format

| D <sub>7</sub>  | D <sub>6</sub> | D <sub>5</sub>  | D <sub>4</sub>  | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | Do  |

|-----------------|----------------|-----------------|-----------------|----------------|----------------|----------------|-----|

| SC <sub>1</sub> | SC0            | RW <sub>1</sub> | RW <sub>0</sub> | M <sub>2</sub> | M <sub>1</sub> | Mo             | BCD |

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへぐ

#### BCD :

| 0 | Binary counter 16 - bits                          |  |  |

|---|---------------------------------------------------|--|--|

| 1 | Binary coded decimal (BCD)<br>Counter (4 Decades) |  |  |

#### 8254 Counter Modes

- Mode 0 (Interrupt On Terminal Count )

- Mode 1 (Hardware retriggerable Monoshot )

- Mode 2 (Timed interrupt Generator)

- Mode 3 (Square Wave Generator )

- Mode 4 (Software Triggered Strobe )

- Mode 5 (Hardware Triggered Strobe )

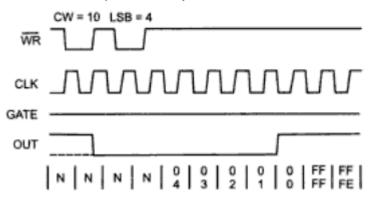

- The output becomes a logic 0 when the control word is written remains low even after count value loaded in counter.

- Counter starts decrementing after falling edge of clock The OUT goes high upon reaching the terminal count and remains high till reloading OUT can be used as interrupt

- Writing a count register , when previous counting is in process

- first byte when loaded stops the previous count,

- second byte when loaded starts new count

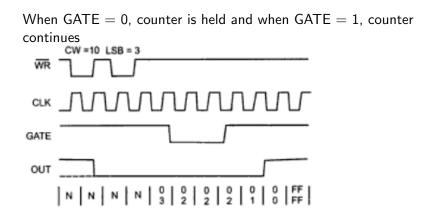

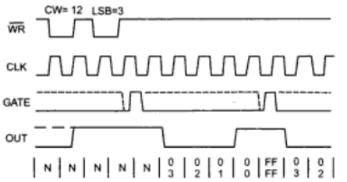

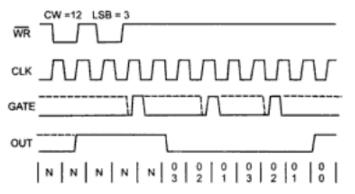

- Gate high = normal counting

- Gate low = counting terminated and current count latched till GATE goes high again

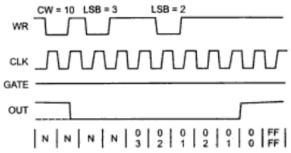

Assuming, CW = 10; counter 0 initialized for binary counting, mode 0 and read/write of only LSB

If new count is written, counter is loaded with this value in the next clock pulse

- Gate input is used as trigger input

- Output remains high till the count is loaded after application of trigger, output goes low and remains low till count becomes zero

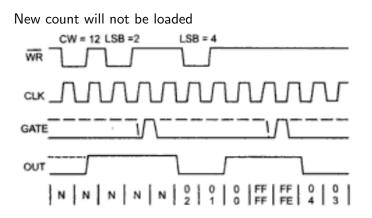

- Another count loaded, when output already low, it does not disturb counting until a new trigger is applied at the gate

• New counting starts after new trigger pulse

For mode 1 GATE act as trigger input, When GATE =1 count is transferred from count register to actual counter

This waveform demonstrates retriggerable behavior If another trigger pulse comes, the count is reloaded and output will remain low

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ ─臣 ─のへで

#### Do it yourself

Assignment - 2

Study all the other 5 modes and prepare a document which will contain theory and related figures.

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへぐ

# STRAWBERRY

[] /strawberrydevelopers

[] /strawberry\_app

For more visit:

Strawberrydevelopers.weebly.com